Introduction to Latch Logic

The Latch/Unlatch instructions are retentive. This means that once the latch instructions goes true, the bit remains ON. Even when the instruction goes false, the bit will still remain a 1 until we unlatch the bit. Also, if we take the processor to program mode, or it looses power, the bit will still remain on. For this reason, it’s not recommended to use the latch instruction on prime movers such as a motor or solenoid.

The latch instruction can be used to represent the fact that the equipment has reached a certain state in a cycle. This way, when the processor comes back up, it will “remember” in what state it left off. The latch is also used for warning or alarm indicators, so the bit will remain latched until the operator clears the latch (unlatching the bit).

You will find the Latch and Unlatch instruction on the Instruction toolbar. Notice the last two instructions on the favorites tab (by default). You will also find these instructions on the BIT tab of the Instruction toolbar.

![]()

Logic Rungs

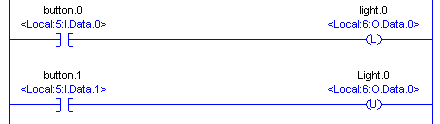

Here, we have our two rungs of logic:

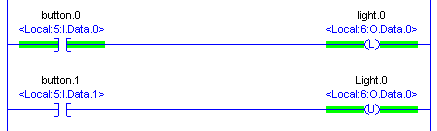

When you press button, 0, Light 0 will be energized. Notice the way that both the latch and the unlatch instructions are intensified when light.0 changes to the value of 1. This reflects the state of the bit on both the latch and the unlatch instruction

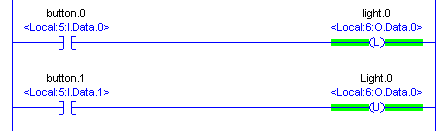

Next, notice what happens when we let go of button.0. Light.0 still remains energized, even though the line of logic is false.

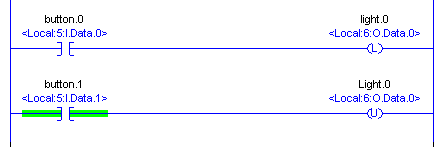

Now we’ll press button1. This will unlatch our bit. You will notice that when we have continuity to the unlatch instruction, the bit shuts off.

If both the latch and unlatch are made at the same time, usually the unlatch will win. This is because your processor reads logic just like you read a book… Left to right, top to bottom. Due to the asynchronous scan of the ControlLogix though, it’s not impossible that the output could energize for a split second if both the latch and unlatch are true at the same time.

For other posts, visit the ControlLogix category page.

— Ricky Bryce