Introduction to ControlLogix File Bit Compare

The ControlLogix File Bit Compare instruction searches for mismatched bit between the source and reference tags. There are several uses for this instruction. One use would be for alarms. We can compare the source value against a reference of 0. in this case, the FBC will log any bits that are high in the source tag. Effectively, this converts bit numbers to an integer value. Another use would be to detect a problem with redundant input modules. If, at any time the two modules do not match, the FBC can log the bit numbers of the mismatched modules.

Generally, there are 2 modes we might use: One mismatch at a time, or all bits. If we want to see all the bits where we have a mismatch, then the result array needs to be at least the same size of the number of bits you are comparing.

Always be sure to do your testing to make sure the FBC will work without causing a hazard before you implement it in any way. Also be sure you don’t inadvertently change data by using this instruction.

Create the Tags

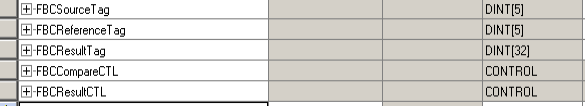

Before we begin, let’s set up some tags, so we don’t have to do this later on.

As you can see, we’ve created 5 new tags. FBCSourceTag and FBCReferenceTag are both an array of 5 DINTs. We’ll only use one of these elements, but we’ll leave some extra room in case we need to compare more data at a future date.

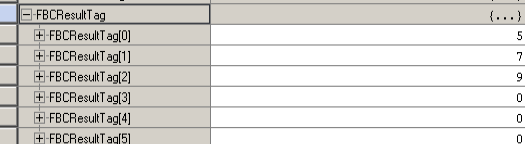

The FBCResult tag is where we log the mismatched bit. Keep in mind, if you are logging all mismatches at once, then this array should be at least as large as the number of bits you are comparing.

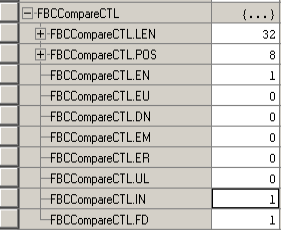

The first control tag is for the instruction to keep track of which bits we are currently comparing. The second control tag is for the instruction to keep track of which element to write to in the result array.

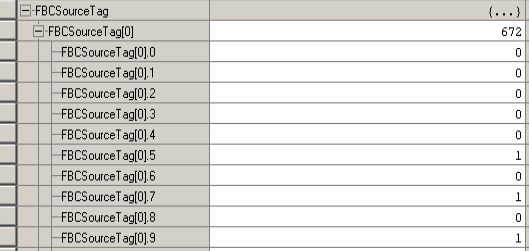

In this case, I will turn on a few random bits in the FBCSourceTag, so we can see if we get the results we expect.

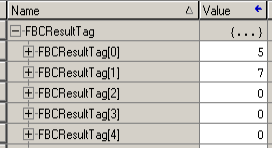

You will see that I’ve turned on three bits: 5, 7, and 9. This might simulate alarm conditions. Our goal is to convert these bit numbers to a numeric value of 5, 7, and 9 in our result array. We might then use these values to display specific alarm messages for the operator. Don’t let the 672 confuse you. This is simply a numeric representation of the bits that are high in this tag. Keep in mind that our goal is to display the specific bit numbers of 5, 7, and 9.

Set up the Logic for ControlLogix File Bit Compare

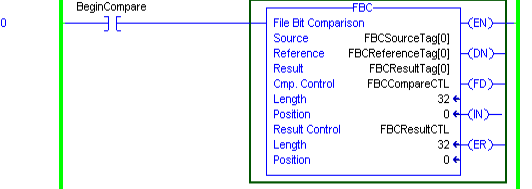

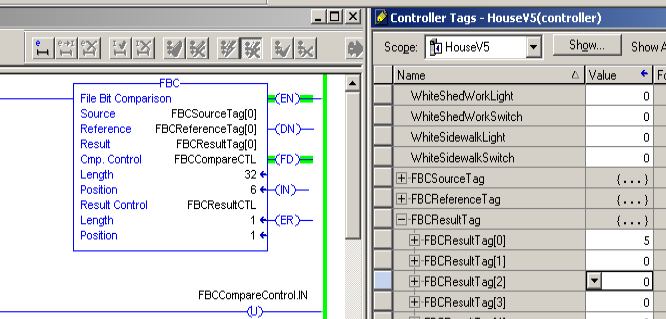

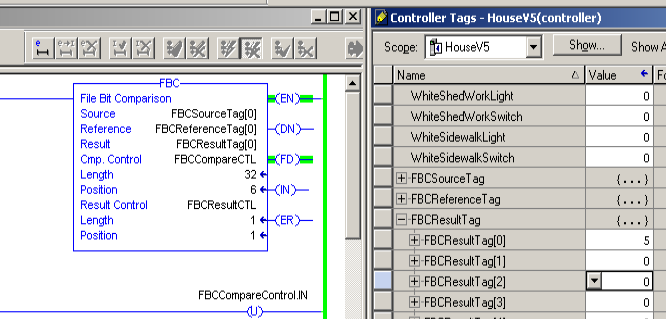

Let’s set up the ladder logic as follows:

As you can see, I’m triggering the FBC with a tag called “Begin Compare”. You might use a real switch, or even a timer instead.

Test the Result — All Bits

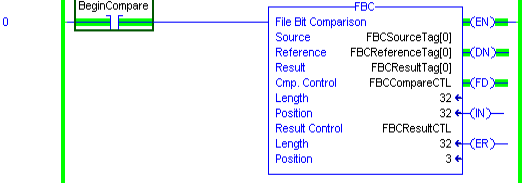

At last, we are ready to check our work. I’m going to toggle the “BeginCompare” Bit. To check all mismatches at once, be sure the IN bit is reset (zero) in the compare control tag.

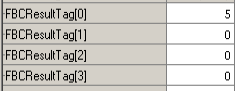

The instruction is done. If you look at the position of the result control file, we are at position #3. This means the instruction found 3 mismatches. Let’s look at the result array, and see if we get what we expect.

FBC Single Compare with result size of 1.

Another way to use the instruction is one single mismatch at a time. I’ll set the result length to 1. After a mismatch is found, we’ll toggle the “BeginCompare” bit off then back on to locate the next mismatch. As you can see, the instruction is not done this time, but the FD (Found) bit is set. In this case, we only logged one mismatch. We have a 5 in the result tag.

If we toggle the “BeginCompare” bit off then back on, we find the next mismatch.

The process continues until the instruction sets the DN bit.

FBC Single Compare Mode (One at a time) with result length of 32.

Another option is to leave the result array at 32, and set the inhibit bit of the compare control tag.

Now, let’s look at the results array. When the rung goes from false to true, the instruction logs the first mismatch only.

To find the next mismatch, I need to toggle the “BeginCompare” bit off then back on. You will see the next mismatch is found.

As you can see, the instruction finds the next mismatch, and logs the position of the mismatch to element 1 of our results array.

This continues until the instruction sets the DN bit. In this mode, you must toggle the rung off then back on every time the instruction finds a mismatch.

For more information on other ControlLogix posts, see the category page!

— Ricky Bryce